# Current Sensing with ICeGaN<sup>™</sup>

## **Overview**

This application note relates to Cambridge GaN Devices (CGD) H2 series devices<sup>1</sup>. It explains why current sensing is required in most power conversion circuits. The document considers the strengths and weaknesses of existing methods and goes on to describe a unique property of CGD ICeGaN devices: that they provide a current sense function without breaking into, and thereby compromising, the high current loop (from supply decoupling capacitor, through the magnetic and device and back to the decoupling capacitor).

Some years ago, International Rectifier produced a (silicon) MOSFET with current sensing [1],[2]. It suffered from an expensive package and a vertical construction. Although the desirability of a power switch which incorporated current sense was clear, it was not commercially successful. However, lateral GaN power devices, like ICeGaN, have an inherent advantage over vertical devices as low-side switches because lateral devices dissipate heat through the grounded source pad. Vertical devices dissipate heat through the switching drain node. The implications of this for current sensing are significant and explained below.

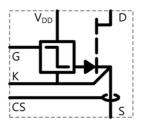

The current sense mechanism in ICeGaN devices (see Figure 1) is described in detail, along with its limitations, performance characteristics and accuracy. There are three ways to use the current sense pin of ICeGaN devices:

- 1. On-state voltage sensing.

- 2. Accurate current sense with zero temperature coefficient.

- 3. Indicative current sense with positive temperature coefficient.

The applications of each function are considered and a range of circuits to process the ICeGaN current sense signal is discussed. The design engineer can then select the appropriate price-to-performance ratio for their needs. Examples of waveforms and components from practical circuits are also presented.

Figure 1 – CGD ICeGaN package and symbol

<sup>&</sup>lt;sup>1</sup> Please contact CGD for questions relating to H1 series devices

## Contents

| Overview                                                                           |  |

|------------------------------------------------------------------------------------|--|

| Contents                                                                           |  |

| Nomenclature                                                                       |  |

| 2 Existing Current Sense Techniques                                                |  |

| 2.1 Resistors                                                                      |  |

| 2.2 Hall-effect Devices                                                            |  |

| 2.2 Hall-effect Devices                                                            |  |

| 3 Current Sensing in Vertical MOSFETs and Lateral GaN HEMTs                        |  |

| 4 Terminating the CS Pin                                                           |  |

| 4.1 Terminating with an "Open Circuit"                                             |  |

| 4.2 Terminating with a Short Circuit                                               |  |

| 4.3 Terminating with a Finite Resistance Value between an Open and a Short Circuit |  |

| 5 Idealised Device Characteristics                                                 |  |

| 5.1 CGD65B240SH2                                                                   |  |

| 5.2 CGD65A/B130SH2                                                                 |  |

| 5.3 CGD65A055SH2                                                                   |  |

| 6 Current Sense Circuit Ideas                                                      |  |

| 6.1 Resistor Circuits                                                              |  |

| 6.2 Operational Amplifier Circuits                                                 |  |

| 6.2.1 Trim Operational Amplifier Output to Correct for Initial Error               |  |

| 6.3 Current Sense Transformer (CST) Circuits                                       |  |

| 6.3.1 Sizing the current sense transformer                                         |  |

| 6.3.2 Adding a Synchronous Rectifier                                               |  |

| 6.4 Setting the signal voltage and temperature coefficient                         |  |

| 6.5 Transformer and operational amplifier circuits                                 |  |

| 6.6 Forced Current Sharing                                                         |  |

| 6.7 Full Bridge                                                                    |  |

| 7 Waveforms                                                                        |  |

| 8 Other Considerations                                                             |  |

| 8.1 Errors                                                                         |  |

| 8.2 Sensing reverse current flow                                                   |  |

| 8.3 Sensing in high side devices                                                   |  |

| 8.4 CS unused                                                                      |  |

| 8.5 Maximum v <sub>Cs</sub> Voltage                                                |  |

| 8.6 Monitoring On-State Voltage                                                    |  |

| 8.7 Maximum resistance                                                             |  |

| 9 Conclusion                                                                       |  |

| 10 References                                                                      |  |

## Nomenclature

| CSR                  | Current Sense Ratio – the current in the Sense HEMT divided by the total current in the drain. This is quoted as a number (without units). |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Current Gain         | As per Current Sense Ratio, but referred to with units of mA / A to convey a sense of scale.                                               |

| d                    | Duty cycle                                                                                                                                 |

| $f_{sw}$             | Switching frequency                                                                                                                        |

| l <sub>cs</sub>      | Current from the ICeGaN CS pin – positive current out of the pin                                                                           |

| I <sub>pk</sub>      | Peak drain current                                                                                                                         |

| Np                   | Primary turns                                                                                                                              |

| Ns                   | Secondary turns                                                                                                                            |

| R <sub>cs</sub>      | A resistor fitted between the ICeGaN CS pin and Kelvin                                                                                     |

| R <sub>DS(on)</sub>  | On-state resistance of a power device                                                                                                      |

| R <sub>Link</sub>    | Parasitic resistance between the source of the Sense HEMT and the CS pin                                                                   |

| R <sub>Sense</sub>   | A current sense resistor driven by a current sense transformer                                                                             |

| $R_{Apparent}$       | The apparent resistance of R <sub>Sense</sub> as seen from ICeGaN CS pin                                                                   |

| R <sub>0QA,J-C</sub> | Junction to case thermal resistance of Q <sub>A</sub>                                                                                      |

| $R_{\theta QA,C-A}$  | Case to ambient thermal resistance of Q <sub>A</sub>                                                                                       |

| T <sub>amb</sub>     | Ambient temperature                                                                                                                        |

| T <sub>C</sub>       | Device case temperature                                                                                                                    |

| ΤJ                   | Device junction temperature                                                                                                                |

| V <sub>CS</sub>      | The CS pin voltage relative to Kelvin                                                                                                      |

| V <sub>CS_pk</sub>   | The peak value of v <sub>CS</sub>                                                                                                          |

| V <sub>DS</sub>      | drain-source voltage                                                                                                                       |

## **1** Introduction

Power conversion circuits process energy. To control the flow of energy, power conversion control circuits normally require inductor current and / or capacitor voltage as control inputs. The most popular control method is current-mode which always requires a measure of the inductor current. In many switched power conversion circuits the controlled switch is in series with the inductor; the inductor current can therefore be measured by sensing the switch current. ICeGaN offers an elegant new way of doing this, and in many ways is the ideal low-side switch for current-mode controlled circuits.

In this application note we will briefly consider existing current sensing techniques. Current-mode-controlled circuits need to measure large, high-bandwidth current signals accurately which brings a number of challenges. These challenges will be the subject of **Section 2** and the following sections will explain how they are addressed by ICeGaN.

**Section 3** will describe the internal construction of ICeGaN and outline its strengths as a low-side, current-mode switch.

**Section 4** will outline the options for terminating the CS pin.

**Section 5** gives idealised characteristics of ICeGaN H2 devices for the design engineer. It illustrates how the current sense function varies with junction temperature.

**Section 6** contains application circuit ideas. It explains how the initial tolerance of the current sense can be trimmed out in precision circuits, and how the temperature coefficient of the signal and the signal amplitude can be independently set.

**Section 7** shows waveforms from a CGD 65 W quasi-resonant flyback evaluation board which uses a miniature current transformer to translate the signal level.

Section 8 provides a quick reference of CS pin properties for designers.

We conclude this application note with **Section 9**.

## 2 Existing Current Sense Techniques

This section briefly discusses existing current sense options for power circuit designers.

#### 2.1 Resistors

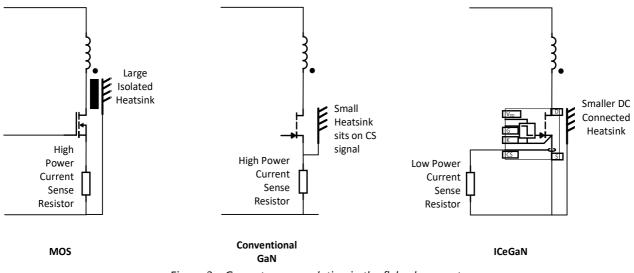

Resistors are the simplest, cheapest and, with a high specification component, the most accurate solution. Lowinductance resistors are available that can measure accurately with a high-bandwidth. Unlike a transformer, they are not Volt-second limited and can therefore measure dc signals. However, generating a signal which is big enough to be measured accurately in the presence of noise wastes power and this technique is better suited for low-power designs. The signal is not isolated, and it is not always possible to refer the signal easily to the control reference. A resistor requires space to dissipate heat and increases the high-current loop area thereby compromising the design. Placed in the source of a power switch, it often subtracts from the gate-source voltage as shown in *Figure 2*.

#### 2.2 Hall-effect Devices

Hall-effect devices offer dc and ac measurement without breaking the high current loop, but the loop often has to be extended to pass through a Hall-effect Device. Hall-effect devices are comparatively expensive, suffer from offsets, high temperature coefficients and limited bandwidth. Moreover, they can be prone to errors caused by stray magnetic fields. They tend to be used in higher power designs and where isolation is required.

#### 2.3 Current Sense Transformers

Current sense transformers are normally combined with a resistor and found in low-cost circuits like fluorescent lamp ballasts and high-accuracy circuits like electricity meters. The transformer offers a low-cost isolated measurement with a fast signal which is not bandwidth limited for practical purposes. However, a single transformer cannot make a dc measurement. A dc signal must be constructed by summing at least two pulses from different transformers. There is always an inherent error due to magnetising inductance; the bigger (and more expensive) the transformer, the smaller the error.

All these existing techniques have applications where, in the past, they offered the least-worst option. ICeGaN devices offer the designer a new technique which involves sampling the inductor current without the need to fit a dedicated measurement device into the pulsed current loop. The following sections explain how this is achieved.

## **3** Current Sensing in Vertical MOSFETs and Lateral GaN HEMTs

Current sensing in a low-cost off-line flyback normally relies on measuring the full load current, often with a resistor. See *Figure 2*. This is not ideal because the resistor is dissipative and conducts the full load current. The resulting signal is small, noise-sensitive, and referred to both power and signal grounds. The integrity of the signal is dependent on a good star point between the two grounds on the PCB layout.

Vertical devices, such as MOSFETs, have a crucial disadvantage as a low-side switch when compared to lateral devices. The heat must be extracted through the high-voltage switching node. This means the MOSFET device tab must be insulated before being connected to a heatsink; the resulting heatsink is therefore bigger than it needs to be.

*Figure 2 – Current sense evolution in the flyback converter*

Lateral GaN HEMTs have an important advantage over MOSFETs as a low-side switch because the heat is extracted through the low-voltage source terminal.

A flyback converter built with a conventional GaN HEMT extracts the heat from the source net, on top of the current sense resistor. The copper area on the net connecting HEMT source to sense resistor is always smaller than the ground plane thereby limiting the heatsinking capacity of the power HEMT. Furthermore, conventional GaN HEMTs have a much lower gate threshold voltage than MOSFETs and the noisy voltage generated across the source resistor subtracts from the gate voltage in an unpredictable way. For example, a HEMT which requires a gate drive signal between 5 to 6 Volts, would lose close to 1 V of gate drive across the sense resistor at full load. That is a significant proportion of the drive signal.

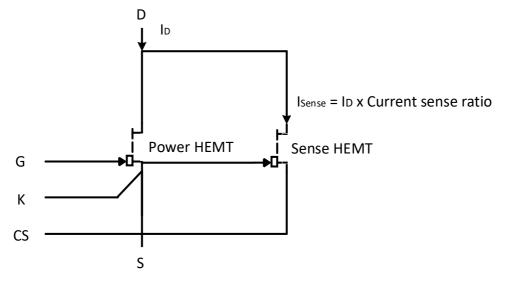

*Figure 2* and *Figure 3*, both illustrate how ICeGaN samples the current signal, making it available to the designer at the CS pin. ICeGaN interfaces elegantly between the power and signal grounds using an internal Kelvin connection which helps to keep the signal-to-noise ratio high. Crucially, ICeGaN allows the main heatsink tab to be connected directly to the copper of the ground plane. In low power converters this is often enough to eliminate the need for a discrete heatsink. If additional heatsinking were required, it can connect directly to the ground plane; there is no need for a direct interface between device and heatsink. Eliminating a discrete heatsink enables higher density power circuits, more automated assembly, and therefore lower assembly costs and better yields. The voltage generated on the CS pin is always less than v<sub>DS</sub> and not large enough to compromise the gate drive of the sense HEMT.

Figure 3 - ICeGaN structure. Main HEMT on the left and parallel sense HEMT on the right.

ICeGaN incorporates a Kelvin connection to optimise the star point connection of the signal and power grounds and avoids the need to measure the full inductor current by taking instead a small sample. It is helpful to have two ways of quantifying the size of the sample. The current sense ratio (CSR) is defined as the current in the Sense HEMT divided by the current in the drain, and reduces as the device size increases.

$$CSR = \frac{I_{Sense}}{I_{Drain}}$$

Equation 3-1

Current gain is the same figure but referred to with units of mA / A to convey a sense of scale. The sampled drain current can then be used to generate a voltage for the controller. As a result, the main HEMT in the ICeGaN package sees the full applied gate-driver voltage from the controller, whilst a parallel Sense HEMT only sees a small reduction in its gate voltage. The improvement from the MOSFET circuit in *Figure 2* to the ICeGaN circuit is immediately apparent.

Other sensing devices are also used in high power circuits, like a Hall-effect or current transformer. They tend to be large, expensive and must be inserted in the pulsed power loop. This makes the loop bigger, increases parasitic inductance and therefore noise. It is difficult to measure the full load current without compromising the circuit.

This section has explained the advantage of integrating current sense in the HEMT. The next section describes different ways to use the flexibility of the ICeGaN CS pin.

## 4 Terminating the CS Pin

There are three ways to terminate the CS Pin.

- 1. An open circuit.

- 2. A short circuit.

- 3. A finite resistance value between an open and a short circuit.

This section describes the resulting performance.

#### 4.1 Terminating with an "Open Circuit"

When the CS pin is left "open circuit" (see section 8.7 for qualification), current through the CS pin is zero. When the ICeGaN gate is high, the voltage drop across the sense HEMT drain-source terminals is zero and the CS pin becomes a way to sense the on-state voltage of the main device with a low voltage circuit.

This has a number of potential uses:

- Checking dynamic R<sub>DS(on)</sub> effects.

- Checking for device saturation.

- Measuring device power dissipation.

#### 4.2 Terminating with a Short Circuit

When the CS pin is terminated with a short circuit, the main HEMT and the Sense HEMT are monolithic devices with source and drain terminals connected. As a result, the current sharing is theoretically constant over temperature and the temperature coefficient of the ICeGaN device current gain is close to zero. Small variations remain due to  $R_{Link}^2$  and process variations.

The initial tolerance of the current gain is process dependent. At the time of writing, it is between  $\pm 5\%$  and  $\pm 8\%$ . This technique is recommended for accurate current measurement over temperature, such as:

- Power factor correction circuits.

- Photovoltaic inverters.

- Motor control.

#### 4.3 Terminating with a Finite Resistance Value between an Open and a Short Circuit

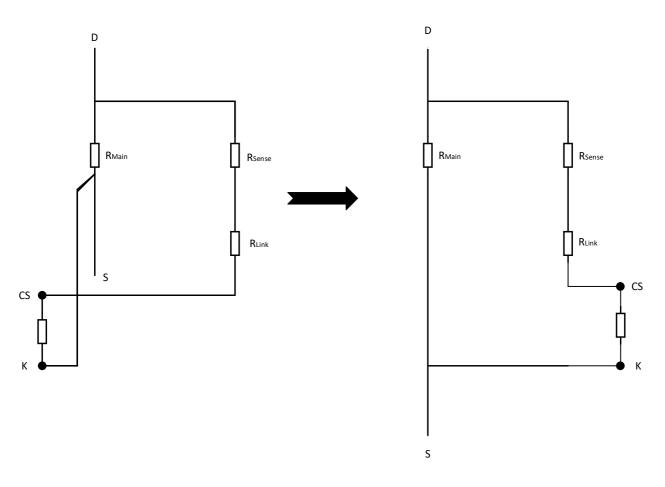

When an external resistor is added between the CS pin and Kelvin, current at the drain node still divides between the two HEMTs according to the ratio of the parallel resistive paths, as shown in Figure 4.

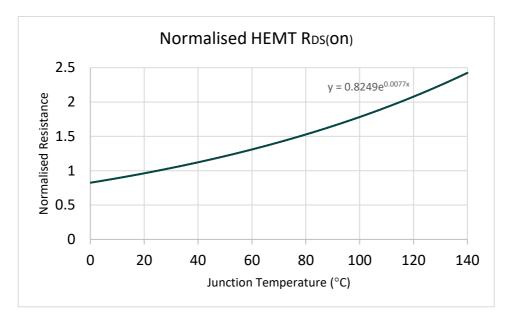

When R<sub>cs</sub> is increased from zero, less current will flow through the Sense HEMT because the resistance of that path is now higher. The current gain will be reduced. The temperature coefficient of resistance for the current path through the series combination of Sense HEMT and external resistor will no longer match the temperature coefficient of the path through the main HEMT. The temperature coefficient of the fixed resistor is much lower than GaN, (See Figure 5). The current gain of the ICeGaN device, therefore, has an increasingly positive temperature coefficient as the external resistor is increased.

<sup>&</sup>lt;sup>2</sup> R<sub>Link</sub> represents the parasitic resistance of the internal connection between the source of the Sense HEMT and the CS pin. It creates a small error term.

The maximum possible CS pin voltage is limited by the device on-state voltage. For system efficiency, it is desirable to have a low on-state voltage. Current-mode controllers normally require a bigger signal voltage on their current sense pins for optimal operation than can be provided by ICeGaN using a simple resistor termination. This often requires some form of signal processing which is discussed below.

Figure 4 - Internal resistances – parallel paths through main HEMT and sense HEMT

Another key point is that as  $R_{cs}$  is increased, the tolerance of the current gain increases and tends toward the tolerance of the device  $R_{DS(on)}$ . We can understand this by considering the two extremes. A short-circuit results in two thermally matched monolithic devices with a tightly matched temperature coefficient. An open-circuit results in measuring the voltage across the main HEMT using the  $R_{DS(on)}$  of the main device as the current sense element.

This positive temperature coefficient of current gain has several potential uses, for example:

- Over temperature protection circuits for device or transformer.

- Forced current sharing in parallel operation.

Figure 5 – Normalised H2 HEMT R<sub>DS(on)</sub> vs junction temperature

The idealised device characteristics discussed in the following section allow the design engineer to estimate current sense ratios in some standard devices.

## **5** Idealised Device Characteristics

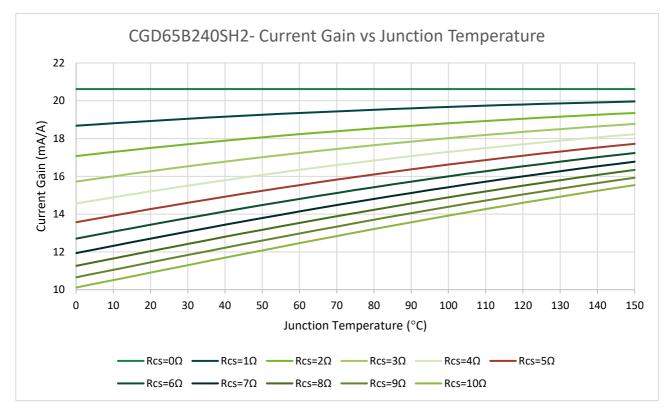

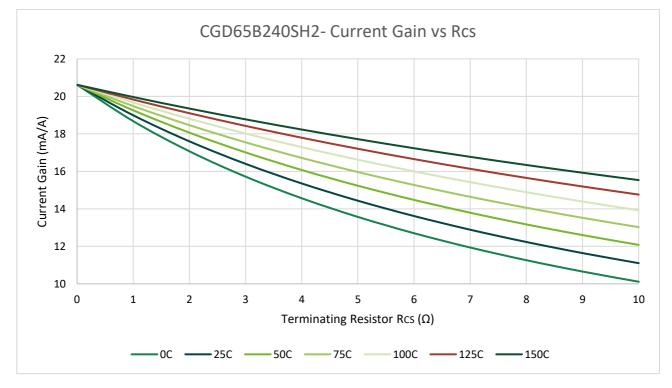

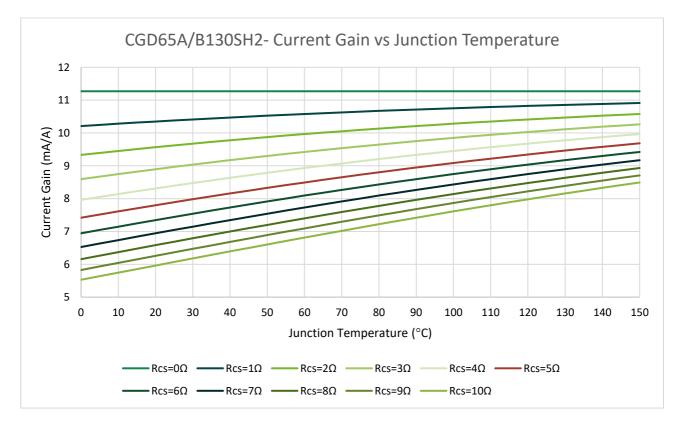

The current gain is measured in milliamps of CS pin current per Amp of total device drain current. The graphs below are calculated using the nominal current sense ratios for CGD H2 devices and ignore the effect of the link resistance (R<sub>Link</sub>) shown in Figure 4.

| ICeGaN Device | Nominal $R_{DS(on)} / m\Omega$ | Current Gain (R <sub>cs</sub> =0) / mA/A |  |

|---------------|--------------------------------|------------------------------------------|--|

| CGD65B240SH2  | 240                            | 20.6                                     |  |

| CGD65A130SH2  | 130                            | 11.3                                     |  |

| CGD65B130SH2  | 130                            | 11.3                                     |  |

| CGD65A055SH2  | 55                             | 7.6                                      |  |

### 5.1 CGD65B240SH2

Figure 6 - CGD65B240SH2- Current Gain vs Junction Temperature

Figure 7 - CGD65B240SH2- current gain vs Rcs

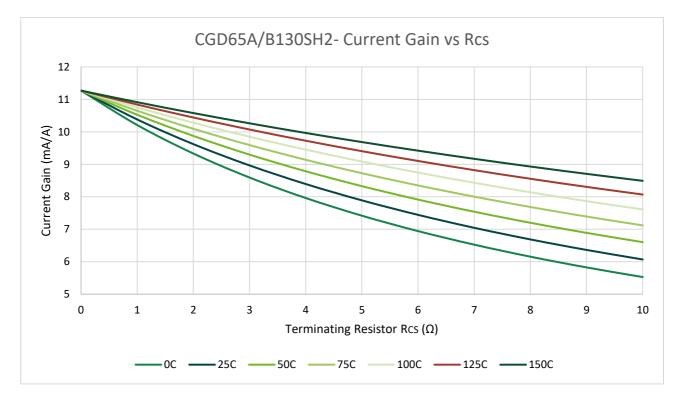

### 5.2 CGD65A/B130SH2

Figure 8 - 130 m $\Omega$  current sense ratio mA/A vs junction temperature

Figure 9 - CGD65A/B130SH2- current gain vs Rcs

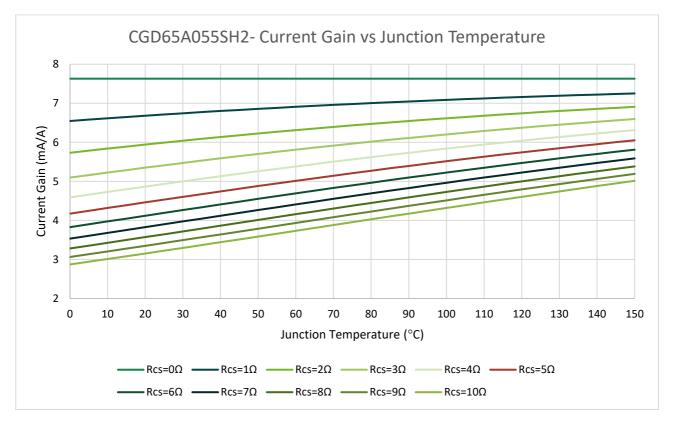

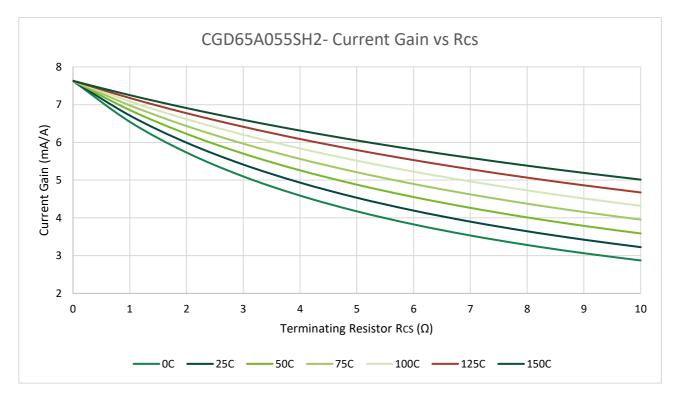

### 5.3 CGD65A055SH2

Figure 10 - CGD65A055SH2- current gain vs junction temperature

Figure 11 - CGD65A055SH2- current gain vs Rcs

## 6 Current Sense Circuit Ideas

This section considers how best to terminate the CS pin for different applications. To recap, there are three ways to terminate the CS pin:

- 1. Short circuit to Kelvin > "zero" temperature coefficient signal

- 2. Open circuit to Kelvin -> On-state voltage sensing

- 3. An intermediate resistor value between CS pin and Kelvin -> Positive temperature coefficient signal

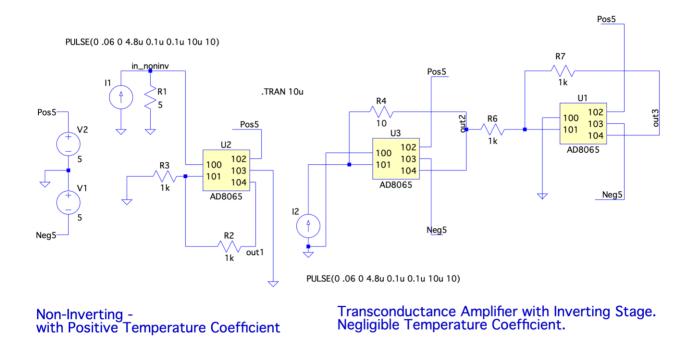

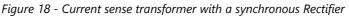

If we want to minimise the measurement temperature coefficient, an operational amplifier is required, and is configured as a transconductance amplifier directly converting current to voltage as shown by Figure 12.

Figure 12 - Spice simulation of non-inverting, transconductance and inverting current sense circuits

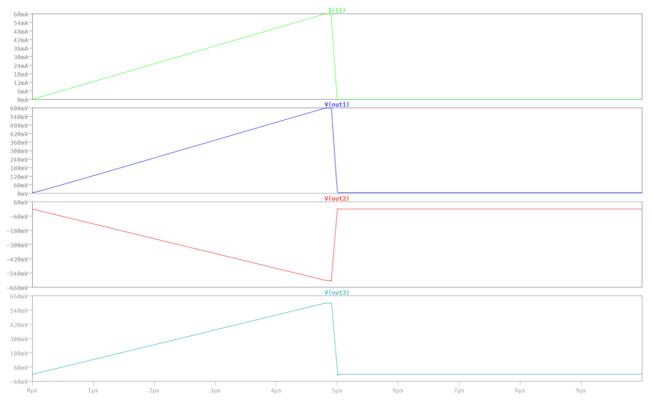

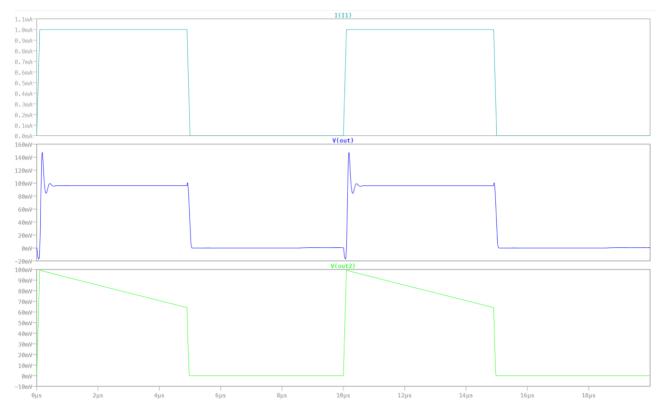

Figure 13 - Simulated operational amplifier waveforms

When terminating the CS pin with a finite resistor value, there are two key parameters to set.

- The voltage signal level.

- The temperature coefficient.

A desired positive temperature coefficient can be achieved with a given resistor value. Then the signal is amplified or transformed by a non-inverting amplifier (Figure 12) or miniaturised current sense transformer (Figure 16) to achieve the required signal level.

It was apparent from *Figure 4* that the voltage signal level at the CS pin will always be less than the on-state voltage of the main device. Many circuits will require a higher voltage, and the following circuits show some of the ways this can be achieved.

#### 6.1 Resistor Circuits

As mentioned above, terminating the CS pin with a resistor may well not generate enough signal voltage for satisfactory operation of the controller. Many controllers require signal voltages close to 1.0 V at full load operation. Terminating the CS pin with just a resistor allows no ability to select signal level and the desired temperature coefficient independently. Whilst it may just be possible to make a circuit work with a single resistor, and this will be the cheapest option, it will not work for every application.

#### 6.2 Operational Amplifier Circuits

Operational amplifier circuits can be configured as having a positive temperature coefficient, or a negligible temperature coefficient in which the CS pin is held at the Kelvin potential. See Figure 12.

The simulation in Figure 12 is set up with current sources which ramp up from zero to 60 mA over 4.8  $\mu$ s, remain at 60 mA for 100 ns and then fall to zero over 100 ns. In the CGD65B240SH2, 60 mA from the current sense pin corresponds to 2.9 A of drain current. The non-inverting arrangement on the left uses a 5  $\Omega$  resistor to generate a significant positive temperature coefficient. The circuit on the right uses a transconductance amplifier to change the current sense output to a negative-going voltage whilst keeping the CS pin at Kelvin potential. It produces a temperature coefficient close to zero. The corresponding waveforms are shown in Figure 13. They faithfully represent the shape of the current pulse.

A challenge for a transconductance amplifier is that the operational amplifier needs a small negative supply voltage, and it needs to be present on the first pulse. See Figure 14.

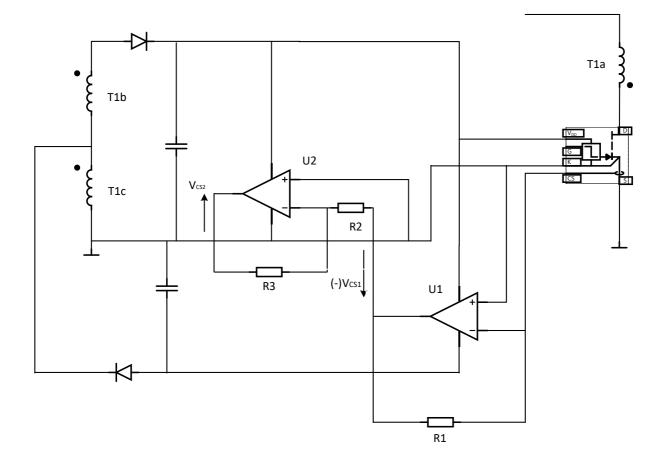

Figure 14 - Basic operational amplifier circuit

Referring to Figure 14, the first amplifier generates a negative going current signal given by:

$$V_{CS1} = R1. I_{Sense.}$$

Equation 6-1

Typical figures might be 60 mA from the CS pin through R1. Making R1 10  $\Omega$  would give a V<sub>CS1</sub> voltage of -600 mV.

Many power factor correction circuits require a negative-going current sense voltage. If a positive signal is required, a dual amplifier can be used, with a second amplifier in inverting configuration.

A small negative supply (~ 2 V) is required to allow the first amplifier to drive negative and this is derived from a peak detector, as shown in Figure 14, from the auxiliary supply.

#### 6.2.1 Trim Operational Amplifier Output to Correct for Initial Error.

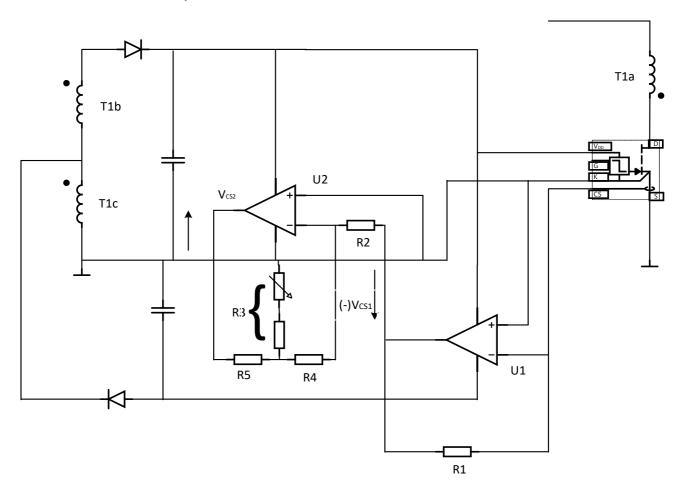

Trimming out the initial offset error, as shown in Figure 15, allows for a very accurate current sense circuit using ICeGaN. Set R4 to allow about  $\pm$  12% adjustment around a nominal value.

Figure 15 - Trimmable operational amplifier circuit

$$V_{CS2} = \frac{V_{CS1}}{R_2} (R5 + R3||R4).$$

Equation 6-2

### 6.3 Current Sense Transformer (CST) Circuits

Current sense transformers solve many problems for the designer. They can incorporate isolation and they scale the signal precisely. (The current is scaled by an integer turns ratio.)

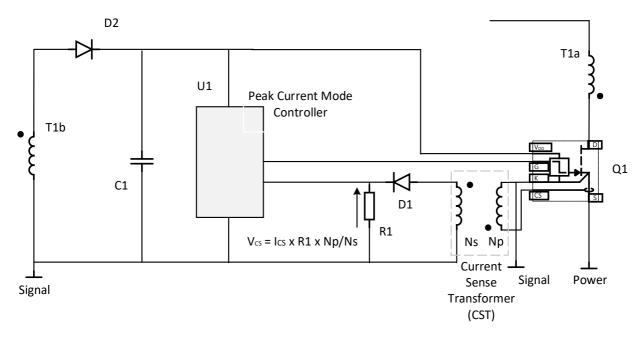

The simplest type of current sense transformer circuit is shown in Figure 16. It incorporates a diode, D1, which allows the transformer to reset. It is important to understand the impact of this diode on circuit performance.

Figure 16 - Simple transformer circuit

The voltage across the current sense transformer secondary is the  $v_{CS}$  voltage added to the D1 diode drop. The size of a current sense transformer is determined by the Volt-second product applied to the secondary winding, meaning that the presence of the diode significantly increases the size of the required transformer. The diode drop also increases the voltage reflected back from secondary to primary winding such that the apparent resistance,  $R_{Apparent}$ , seen by the ICeGaN device increases. However, the signal level  $V_{CS}$  presented to controller, U1, by the current sense transformer is unaffected by the presence of the diode drop.

To summarise, the presence of the diode drop in the circuit will change the apparent resistance seen by the ICeGaN device and therefore the temperature coefficient of the current sense measurement. It will increase the size of the required transformer, but will not affect the signal magnitude. The diode can be replaced by a synchronous rectifier as described in the subsection **Adding a Synchronous Rectifier** below.

#### 6.3.1 Sizing the current sense transformer

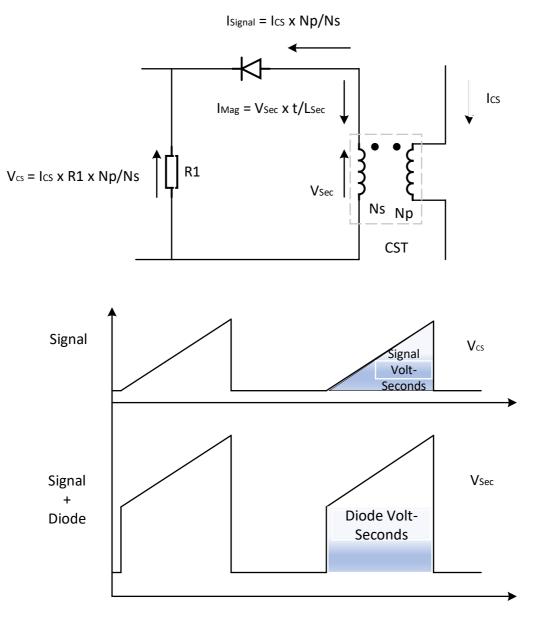

The current sense transformer has an inherent error mechanism. See Figure 17. The secondary current is a combination of the desired signal current minus the magnetising current.

- The signal current (I<sub>signal</sub>) is the CS pin output current scaled by the turns ratio.

- The magnetising current  $(I_{Mag})$  is generated by any voltage that forms across the secondary winding.

The magnetising current component is an error which can be minimised by:

• Minimising the voltage-seconds across the transformer secondary, for example, by using a synchronous rectifier, using an operational amplifier to set the secondary voltage to zero, or raising the frequency.

- As an example, consider a circuit in which the transformer secondary has to support a voltage that rises linearly from zero to 1.0 V over 5  $\mu$ s. The Volt-seconds required for the transformer is the area under the triangle:  $\frac{1}{2} \times 1.0 \times 5 \mu$ s = 2.5 V $\mu$ s. The voltage across the diode adds 0.7 V  $\times 5 \mu$ s = 3.5 V $\mu$ s. The diode more than doubles the requirement.

- Maximising the inductance of the secondary winding. It is normal to use a high permeability ferrite core for current sense transformers. Toroidal transformers are often preferred because a small gap cannot be inadvertently introduced in the magnetic structure when two core halves are assembled.

The designer can therefore size the transformer according to their requirements and may choose to use a bigger transformer to reduce circuit complexity.

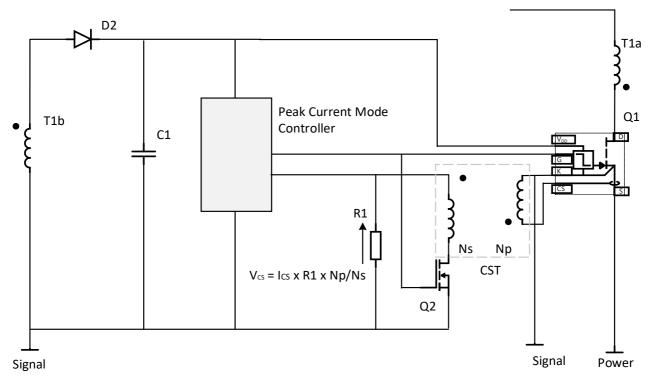

#### 6.3.2 Adding a Synchronous Rectifier

The size of the current sense transformer is determined by the secondary volt-second product. If the desired signal voltage is less than one Volt, adding a diode drop in series can more than double the Volt-second hold-off required of the current

sense transformer. Fortunately, it is possible to eliminate the need for a rectifier diode by adding a small MOSFET to function as a synchronous rectifier as shown in Figure 18. The synchronous rectifier only needs to turn on when the main HEMT is on and therefore can use the same gate drive signal as the main device.

#### 6.4 Setting the signal voltage and temperature coefficient

The designer can set the sense resistor R1, and the turns ratio to give the desired temperature coefficient. The apparent resistor R<sub>Apparent</sub> at the CS pin is given by:

$$R_{Sense} \times \left(\frac{N_p}{N_s}\right)^2 = R_{Apparent}.$$

Equation 6-3

If the desired voltage at the controller is  $v_{cs_pk_r}$  for a device drain current of  $I_{pk_r}$  then:

$$V_{cs\_pk} = R_{Sense} \times \left(\frac{N_p}{N_s}\right) \times CSR \times I_{pk.}$$

Equation 6-4

If the desired temperature coefficient for a design corresponded to an apparent resistance of 1  $\Omega$ , the peak device current to 3.6 A, the desired peak voltage on the controller current sense pin was 0.6 V and the Current Sense Ratio of the device was 1/60, then:

$$v_{cs\_pk} = R_{Apparent} \times \left(\frac{N_s}{N_p}\right) \times CSR \times I_{pk}.$$

Equation 6-5

$$0.6=1\times \left(\frac{N_s}{N_p}\right)\times \frac{1}{60}\times 3.6.$$

Equation 6-6

$$\frac{N_s}{N_p} = 10.$$

Equation 6-7

The sense resistor required would generate 0.6 V with a current of:

$$I_{pk} \times CSR \times \frac{N_p}{N_s} = 6 \ mA_{.}$$

Equation 6-8

This allows the designer to set the desired temperature coefficient / accuracy which then defines the current sense transformer turns ratio.

### 6.5 Transformer and operational amplifier circuits

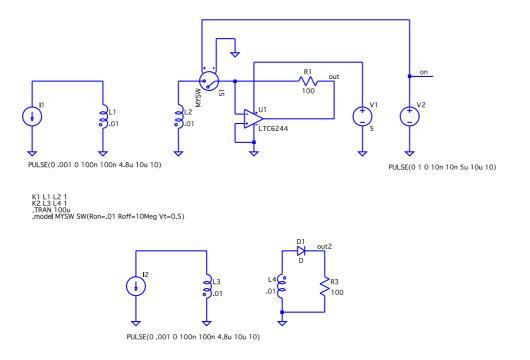

The advantages of transformers and operational amplifiers can be combined if greater circuit complexity is appropriate. See Figure 19. For example, if an isolated signal is required with zero temperature coefficient a transformer can be used to isolate the signal and an operational amplifier to sense the transformer secondary current without applying voltage across the transformer.

The operational amplifier removes the need for the transformer to support Volt-seconds; the transformer can therefore be miniaturised. A trimmer resistor could be added to the operational amplifier circuit as above for increased initial accuracy.

Figure 19 models two circuits measuring a 1 mA pulse. The first uses a 1:1 transformer with primary and secondary inductances of 10 mH. The second uses the identical transformer with a rectifier and resistor output. Both circuits should produce 100 mV across their respective 100  $\Omega$  resistors corresponding to the 1 mA current to be measured. It can be seen in Figure 20 that the operational amplifier circuit does produce a 100 mV output. On the other hand, the transformer circuit produces an initial 100 mV followed by the combination of the 1 mA signal and the transformer magnetising current as defined in Figure 17.

The Volt-seconds across the transformer secondary caused by the diode and resistor create an error that is not present in the operational amplifier circuit. The problem can be addressed by using a bigger current sense transformer to reduce the error to an acceptable level. This could add material cost, reduce the labour cost of miniaturisation, or both. The engineer must compare circuit cost and complexity against the required accuracy.

Figure 19 - Spice simulation of current transformer circuit with operational amplifier

Figure 20 – Simulation results for transformer and transformer/ operational amplifier circuits. Top – Current source to be measured. Middle – Output of operational amplifier circuit. Bottom – Output of transformer-rectifier-resistor circuit.

### 6.6 Forced Current Sharing

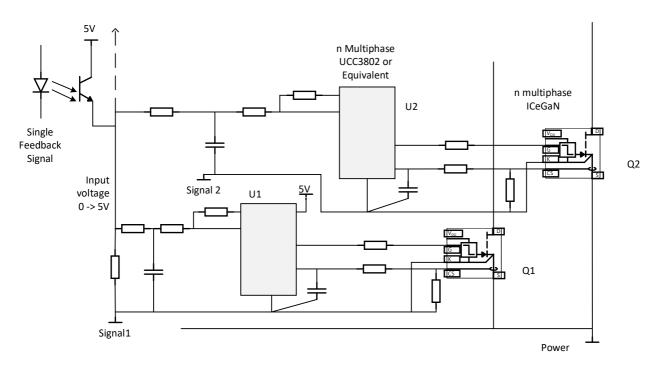

This circuit utilises synchronised low-cost current-mode controllers to set the same peak current for parallel multiphase power converters. It is easy to synchronise these controllers by pulling down on the oscillator pin. Note that grounding has to be handled carefully and connected at one point only. In this case, the grounds are connected at the source terminals and the Kelvins are not connected. The feedback signal is re-referred to the second signal ground through a low pass filter as shown in Figure 21.

Figure 21 - Multiphase devices using current sense

Using a resistor on the CS pin gives a desirable positive temperature coefficient along with overtemperature protection.

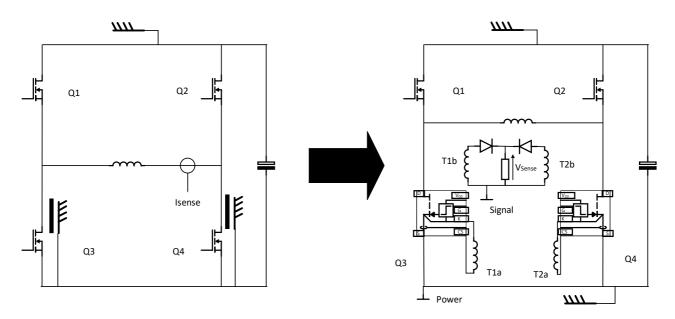

### 6.7 Full Bridge

In full bridge circuits, the CS pins of the low-side devices often provide all the control information required. ICeGaN devices can replace MOSFETs as the low-side devices in full bridge circuits, reduce the heatsinking requirement and provide the current sensing function.

Note that system grounding requires careful thought for each application.

*Figure 22 - Full bridge showing how to reduce the size of low-side heat sinks and eliminate the bulky current-sensing device.*

## 7 Waveforms

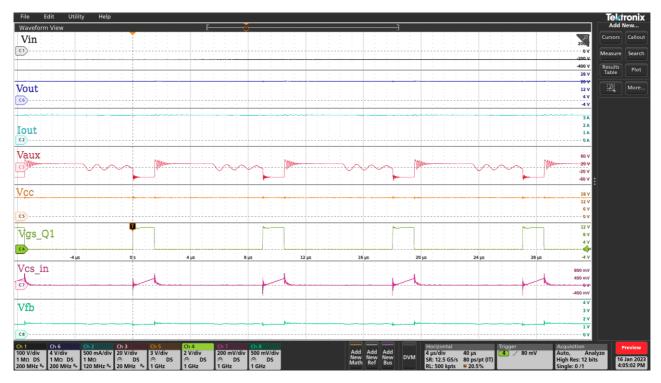

Figure 23 shows waveforms for the CGD 65 W Quasi Resonant Evaluation Board which uses the circuit of Figure 18 to minimise the size of the current sense transformer required. At this power level, the cost of the current sense transformer, see Figure 24, or the operational amplifier solution, is easily offset by a simpler thermal design.

As the device current rating increases, the current gain gets smaller and the sense current does not increase in proportion to device size.

Figure 23 - The CGD quasi-resonant evaluation board waveforms at full load

### Electrical Specifications @ 25°C

| OCL           | 2000uH Min.@100KHz/0.1V(1-2)  |             |  |

|---------------|-------------------------------|-------------|--|

| D.C.R         | 6Ω Max(1-2)                   | 1Ω Max(4-6) |  |

| CW/W          | 15pF Max.@100KHz/0.2V (1-2:4) |             |  |

| Rated Current | 300mA Max                     |             |  |

| Turn Ratio    | 9:1@ (1-2:4-6)                |             |  |

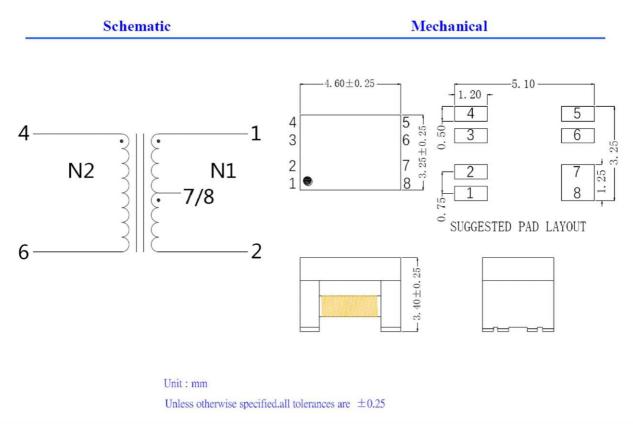

*Figure 24 - Wurth Current Sense Transformer (74930002)*

## 8 Other Considerations

This section covers a miscellaneous selection of ICeGaN device current sensing considerations which have not been covered above.

### 8.1 Errors

$R_{Link}$  is the resistance between the CS pin and the Kelvin star point. It has a different temperature coefficient to the GaN substrate. Even when the CS pin is shorted to the Kelvin pin,  $R_{Link}$  results in a small mismatch of temperature coefficients between the current path through the main HEMT, and that through the series combination of Sense HEMT and  $R_{Link}$ . There is also an initial fixed error in the accuracy of the current gain because of the limitations of the manufacturing process. This is of the order of  $\pm$  5 -> 8 % over process and temperature. For precision current sensing this error should be trimmed out. See Figure 15.

### 8.2 Sensing reverse current flow

If it is necessary to measure the reverse current flow in the device whilst in the off-state, this should always be done with the CS pin at Kelvin potential. The circuit of Figure 14 could be used, for example. The current gain between main device and sense device changes in the reverse direction if  $v_{CS} \neq 0$  V.

### 8.3 Sensing in high side devices

Although ICeGaN makes current sensing easy in a low-side device, sensing current in the source of a high side device is not advised. Sensing current in a high side device always requires isolation to reference the signal to ground potential, and this requires a transformer. The transformer should be placed in the drain connection because it is at a dc potential.

### 8.4 CS unused

When CS is unused, always tie the CS pin to source with a short connection.

### 8.5 Maximum v<sub>cs</sub> Voltage

The voltage between the CS pin and Kelvin should not exceed  $\pm$  1.5 V. Internal diode protection circuitry clamps it to this level.

### 8.6 Monitoring On-State Voltage

If CS is unused, it should be connected to source with a short connection. However, a ground referenced ICeGaN can use the CS pin to monitor the on-state voltage of the main device with a low voltage probe. This can be useful for diagnostic purposes in a laboratory setting and is another unique feature of ICeGaN. Other uses of this functionality are being developed.

The internal diode protection circuitry limits the main HEMT voltage sensing range to less than ± 1.5 V.

#### 8.7 Maximum resistance

When both the main device and Sense HEMT are in the off-state, a fraction of the drain-source leakage current will flow in the sense HEMT. This will generate a voltage across the internal protection diodes. A maximum resistance between CS and Kelvin of 100 k $\Omega$  is therefore recommended.

## 9 Conclusion

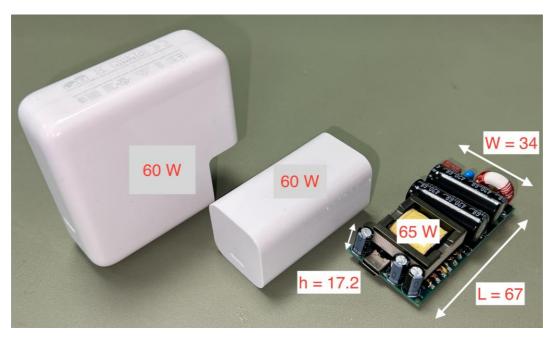

The ICeGaN current sensing feature has been described. Trade-offs involved in current sensing have been considered and it has been demonstrated that power supply designers now have a new option. Whereas vertical devices are inevitably compromised as a low-side switch because the heat must be extracted through the switching node, and conventional GaN devices are isolated from the ground plane by the current sense resistor, ICeGaN allows the heat to be extracted through a soldered connection directly to the ground plane. It is therefore far better suited to applications as a low-side switch than MOSFETs or GaN HEMTs without current sense. It has been shown that this makes ICeGaN particularly well suited to low-cost, high power density designs, see Figure 25. The need for manual assembly of a device to a heatsink with a thermal interface has been eliminated, enabling a reduction in assembly cost and increase in production yields.

Figure 25 - The CGD AR-0065 65 W PD charger on the right next to larger commercial offerings.

ICeGaN current sensing offers the designer a range of temperature coefficients. It has been shown why a low temperature coefficient corresponds to a more accurate initial tolerance and conversely, why a current signal with a positive temperature coefficient has a worse initial tolerance. A low temperature coefficient is required for accurate measurement of current, as in power factor correctors, photovoltaic inverters or motor drives. A positive temperature coefficient is useful for forced current sharing or over-temperature protection. The pin can also be used to access the on-state voltage with a low voltage circuit.

The advantages of being able to measure current in a power switch have been explained, the accuracy and limitations of the feature have been described and the performance of various measuring circuits assessed.

Practical examples of ICeGaN circuits have been presented.

## **10 References**

- [1] S. Clemente, H. Ishii and S.Young, 'An Introduction to the HEXSense<sup>™</sup> Current Sense Device', *International Rectifier Application Note 959B*.

- [2] H. Ishii, S.Young, R.Pearce and D.Grant, 'Using HEXSense™ Current-Sense HEXFETs in Current-Mode Control Power Supplies', International Rectifier, Application Note 961B.

### Author

David Vail Principal Applications Engineer

## Contributors

David Miller Application Engineer

John Findlay Lead Application Engineer

## **Revision History**

| Revision Number | Comments                    | Engineer(s) | Date        |

|-----------------|-----------------------------|-------------|-------------|

| 1.0             | Initial Release             | JF          | 17 Mar 2022 |

| 2.0             | Fully revised for H2 Series | DV          | Nov 2023    |

## Dare to innovate differently

#### **Cambridge GaN Devices Limited**

Jeffreys Building, Suite 8 Cowley Road Cambridge CB4 0DS United Kingdom

in) 🗶) f) 💿) 💊) 🗳

#### Disclaimer

Information presented here by Cambridge GaN Devices Limited is believed to be correct and accurate. Cambridge GaN Devices Limited shall not be liable to any recipient or third party for any damages, including (but not limited to) personal injury, property damage, loss of profits, loss of business opportunity, loss of use, interruption of business, or indirect, special, incidental or consequential damages of any kind in connection with, or arising from, the use or performance of the data herein.

No obligation or liability to the recipient or third party shall arise from Cambridge GaN Devices Limited providing technical or other services. CGD reserves the right to modify the products and/or specifications described herein at any time and at Cambridge GaN Devices' sole discretion. All information in this document, including descriptions of product features or performance, is subject to change without notice.