# **APPLICATION INTERFACE BOARD**

User Guide

CGD-UG2201

#### **Cambridge GaN Devices Limited**

Deanland House 160 Cowley Road Cambridge CB4 0DL

#### Property of Cambridge GaN Devices Ltd.

Copyright© 2022 Cambridge GaN Devices Ltd, 160 Cowley Rd, Cambridge CB4 0DL

Trademarks Registered®. All rights reserved.

Material presented here may not be copied, reproduced, modified, merged, translated, stored or used without prior consent from the copyright owner. All products and groups mentioned are trademarks or registered trademarks of their respective organisations.

### Safety Warning

DANGER: Do not touch the board when high voltages are applied. There are exposed locations of high voltage on the board when connected to a power source. Brief contact may result in serious injury or death. Allow all components to fully discharge before handling the board. This evaluation kit is designed for use by qualified, experienced engineers only. Appropriate safety measures must be put in place before use and the board should never be left unattended.

WARNING: Some components may become hot during operation and remain so afterwards. There is no built in electrical or thermal protection. Operating voltages, currents and temperatures should be monitored closely throughout operation to prevent damage to the board.

CAUTION: This product contains parts susceptible to ESD (electrostatic discharge). ESD prevention procedures must be used while handling the board.

### **Operating Limits and Recommendations**

Operating outside this window is not recommended and may cause damage.

#### **Voltage limits**

The CGD GaN devices have a recommended maximum operation of 650V.

#### **Heat dissipation**

Heatsinking the CGD GaN devices has been provided through bottom side thermal connection to the Application Interface Board (AIB), from top-side to bottom-side of the AIB, then through bottom side thermal connection to the recipient PCB assembly. As a result the thermal stack-up will add contributions  $R_{\theta \text{ TOP-SOLDER}} + R_{\Theta \text{ AIB PCB}} + R_{\Theta \text{ BOT-SOLDER}}$  between  $T_{\text{JUNCTION}} \& T_{\text{AMBIENT}}$ .

#### Start up

It is recommended to apply the low voltage VDD input prior to the application of high voltage inputs.

### **User Guide Overview**

This user guide will outline the Application Interface Board (AIB) and detail how the customer can use the AIB in their own designs. It will explain the AIB construction, electrical connections and how to assemble to the recipient PCB assembly. This guide, along with the AIB itself is targeted at experienced engineers with an understanding of power electronics and appropriate handling techniques. It will assume the competence of the engineer to safely operate the design with exposed high voltages.

### **Target Audience**

This guide, along with the board itself, is aimed at experienced engineers and assumes a knowledge of necessary equipment to analyse the performance of the board. It is designed to enable SMPS engineers, Design Engineers and Technicians involved in the development of a system to rapidly assess the performance of CGD ICeGaN™.

### **Technical Support**

CGD is happy to provide expert help with any questions or problems. For support, please contact CGD at techsupport@camgandevices.com.

## **Revision History**

| Revision Number | Comments        | Engineer(s) | Date       |

|-----------------|-----------------|-------------|------------|

| 1.0             | Initial Release | PC          | 18/03/2022 |

|                 |                 |             |            |

|                 |                 |             |            |

# Contents

| SAFET | TY WAR    | NING                             | 2  |

|-------|-----------|----------------------------------|----|

| OPER  | ATING I   | LIMITS AND RECOMMENDATIONS       | 2  |

|       | Voltag    | ge limits                        | 2  |

|       | Heat o    | dissipation                      | 2  |

|       | Start ι   | ıp                               | 2  |

| USER  |           | OVERVIEW                         |    |

| TARG  | ET AUD    | IENCE                            | 3  |

| TECH  | NICAL S   | SUPPORT                          | 3  |

| REVIS | SION HIS  | STORY                            | 3  |

| 1     | APPL      | ICATION INTERFACE BOARD OVERVIEW | 5  |

|       | 1.1       | AIB Construction                 | 7  |

|       | 1.2       | Electrical Connectivity          | 8  |

| 2     | AIB A     | SSEMBLY                          |    |

| 3     |           | AUTIONS & LIMITATIONS OF USE     |    |

| 4     | AIB C     | ONNECTIVITY                      | 11 |

|       | 4.1       | CGD-ASYINT00101-01 AIB           | 11 |

|       | 4.2       | CGD-ASYINT00201-01 AIB           |    |

|       | 4.3       | CGD-ASYINT00301-01 AIB           | 13 |

|       | 4.4       | CGD-ASYINT00401-01 AIB           | 14 |

|       | 4.5       | CGD-ASYINT00501-01 AIB           | 15 |

|       | 4.6       | CGD-ASYINT00601-01 AIB           | 16 |

|       | 4.7       | CGD-ASYINT00701-01 AIB           | 17 |

|       | 4.8       | CGD-ASYINT00801-01 AIB           | 18 |

|       | 4.9       | CGD-ASYINT00901-01 AIB           | 19 |

|       | 4.10      | CGD-ASYINT01001-01 AIB           | 20 |

|       | 4.11      | CGD-ASYINT01101-01 AIB           | 21 |

|       | 4.12      | CGD-ASYINT01201-01 AIB           | 22 |

| FIGUE | RE LIST . |                                  | 23 |

| APPE  | NDICES    |                                  | 24 |

|       | AIB Va    | ariants                          | 24 |

### 1 Application Interface Board Overview

All MOSFET/HEMTs that have been designed to be mounted to a Printed Circuit Board (PCB) have a footprint & Pin-out that the PCB design must comply with. As many electronic component packages & footprints exist, it is often not possible to remove a MOSFET/HEMT of type 'A' and replace with type 'B', without the need to first redesign the recipient PCB. A process that can drive many months of delay before first use of an alternate device is possible.

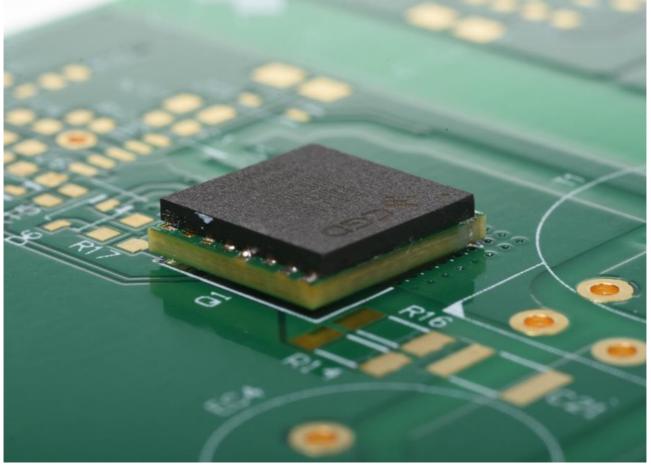

An Application Interface Board 'AIB' is an adaptor PCB that maps each pin/signal from a CGD HEMT device on the topside of the PCB, to each corresponding pin/signal of an alternative component footprint on the bottom side of the PCB. Hence a CGD device equipped with a suitable AIB can easily be fitted using normal soldering techniques to a recipient PCB that was originally designed for an alternative MOSFET/HEMT.

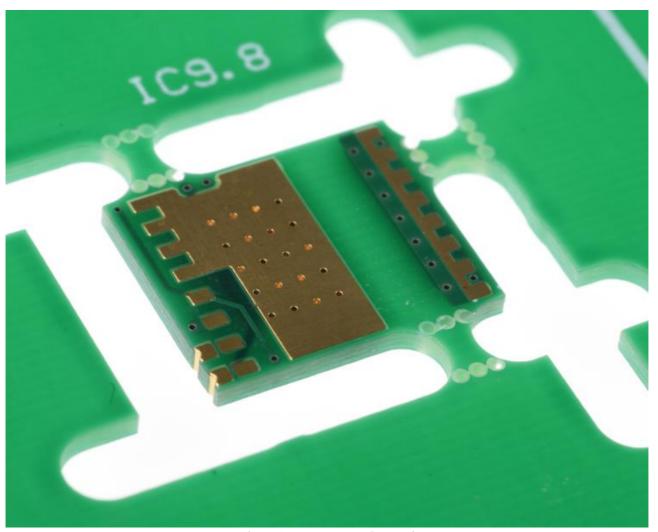

Figure 1 – Bare AIB on PCB Panel

Figure 2 - AIB Mounted to a Recipient PCB Assembly

AIBs are available for all CGD devices and allow their use on recipient PCBs designed around other common PCB footprints/pinouts both SMT & PTH.

The AIB allows 'first assessment' of CGD parts. As the AIB will naturally increase electrical net length and thermal stack-up, the performance will not be optimised and therefore to see the full performance of CGD Devices a PCB redesign will always be required.

#### 1.1 AIB Construction

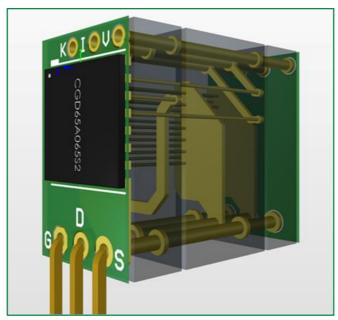

The AIB PCB is manufactured from FR4 and a 35um multi-layer construction. The top-side footprint will be either CGD DFN5x6 or DFN8x8, bottom-side footprint will be as required to match the recipient PCB design and the internal layers will be designed to map between the two pin-outs while minimising electrical parasitics and thermal resistance.

Figure 3 - CGD DFN 5x6 Package

Figure 4 - CGD DFN 8x8 Package

Figure 5 - AIB Construction Showing Internal Layers

#### 1.2 Electrical Connectivity

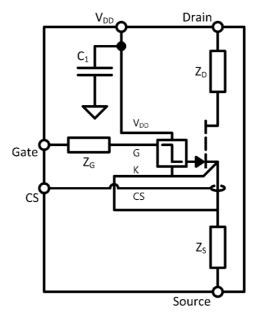

Typical AIB Electrical Schematic is as shown – actual connectivity will vary dependant on the recipient PCB footprint/pinout. All AIB variants contain a VDD decoupling capacitor C1.

Some AIB with use  $V_{DD}$  signal from the receipt PCB footprint when it is present and in these cases  $V_{DD}$  will be provided to the correct ICeGaN<sup>TM</sup> pin by the AIB. In some cases  $V_{DD}$  is not present on the recipient PCB footprint and therefore an alternative  $V_{DD}$  source is required from elsewhere on the recipient design.

In all cases refer to the relevant CGD device data sheet to confirm required connectivity and min/max voltage levels - especially for the  $V_{DD}$  & CS connections.

Note: It is important that  $V_{DD}$  is established prior to application of the device gate signal (turn ON event) – without a valid  $V_{DD}$  the ICeGaN<sup>TM</sup> device will not operate correctly and permanent damage may occur.

Figure 6 - Typical AIB Electrical Schematic

### 2 AIB assembly

During AIB assembly to a recipient PCB, precautions should be taken to avoid any excessive heating of the topside CGD device, decoupling capacitor and connections.

Do not use high melting point solder for the assembly of the AIB Assembly to your application circuit.

Do not exceed maximum re-flow limits as stated below and limit local heating to the underside of the AIB PCB.

| Parameter                    | Conditions   | Min. | Тур. | Max | Unit |

|------------------------------|--------------|------|------|-----|------|

| Reflow soldering temperature | $T_{reflow}$ |      |      | 260 | °C   |

|                              |              |      |      |     |      |

Table 1 - Reflow Parameters for AIB

### 3 Precautions & Limitations of Use

While every effort has been taken to reduce parasitic effects when using an AIB, the traces used to adapt the CGD device connectivity to the chosen interface footprint will add additional impedances to net lengths.

Dependant on how you wish to use ICeGaN<sup>TM</sup>, especially if operating at the limits of performance care should be taken to gradually increase device power level, monitor switching and ensure waveforms are as expected.

Electrical net lengths are increased when using an AIB

- Gate net length is increased by typically 2-6mm.

- Drain net length is increased by typically 1.6mm.

- Source net length is increased by typically 1.6mm.

Care should be taken to consider the additional net lengths in your design and if necessary, adjust performance as required.

Heatsinking the CGD GaN devices has been provided through bottom side thermal connection to the Application Interface Board (AIB), top-side to bottom-side of the AIB, then through bottom side thermal connection to the recipient PCB assembly. Consequently, the thermal stack-up will add contributions  $R_{\theta \ TOP\text{-}SOLDER} + R_{\Theta \ AIB \ PCB} + R_{\Theta \ BOT\text{-}SOLDER}$  between T<sub>JUNCTION</sub> & T<sub>AMBIENT</sub>. Care should be taken to consider this additional resistance in your design and if necessary, adjust performance as required.

## 4 AIB Connectivity

This section details the connectivity of each AIB part number, the pin-out between the devices & any additional connections that are required. In all cases the CGD datasheet should be referenced to ensure compatibility with your circuit/design.

#### 4.1 CGD-ASYINT00101-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate  $V_{\text{DD}}$  AIB side castellation as shown below.

### CGD65A130S2 GS66508B Packaging DFN8x8 mr 10 12 C1 Pin 1 14 Side Castellation 16 C1 Pin 2, Side Castellation

CGD-ASYINT00101-01: GS66508B GaNPX® .. To .. CGD65A130S2 DFN8x8

Figure 7 - CGD-ASYINT00101-01 AIB Pin-Definition

#### 4.2 CGD-ASYINT00201-01 AIB

This AIB does NOT require a separate  $V_{\text{DD}}$  connection from the customer/recipient PCB. The AIB/CGD device takes its  $V_{\text{DD}}$  signal directly from the recipient PCB footprint.

#### CGD-ASYINT00201-01: NV6115 QFN5x6 .. To .. CGD65A130S2 DFN8x8

|                          | CGD65A130S2                     | NV6115                                                | Notes                       |

|--------------------------|---------------------------------|-------------------------------------------------------|-----------------------------|

| Packaging<br>DFN8x8 mm   | 1                               | 5,6,7,8                                               |                             |

| DFN8X8 mm                | 2                               | 5,6,7,8                                               |                             |

| 1-8 Drain                | 3                               | 5,6,7,8                                               |                             |

| 9-12 Source<br>13 Kelvin | 4                               | 5,6,7,8                                               |                             |

| 14 Gate 15 Current Sense | 5                               | 5,6,7,8                                               |                             |

| 16 V <sub>dd</sub>       | 6                               | 5,6,7,8                                               |                             |

|                          | 7                               | 5,6,7,8                                               |                             |

|                          | 8                               | 5,6,7,8                                               |                             |

|                          | 9                               | S                                                     |                             |

|                          | 10                              | S                                                     |                             |

|                          | 11                              | S                                                     |                             |

|                          | 12                              | S                                                     |                             |

|                          | 13                              | NC                                                    | C1 Pin 1, Side Castellation |

| 5                        | 14                              | 2                                                     |                             |

| 9                        | 15                              | NC                                                    | Side Castellation           |

| 16 15 14 13              | 16                              | 1                                                     | C1 Pin 2                    |

| 16 2                     | Notes: NC -<br>NV6115 -<br>C1 - | Not connected<br>Pins 3,4 are NC<br>0.1uF 50V X7R 060 |                             |

Figure 8 - CGD-ASYINT00201-01 AIB Pin-Definition

#### 4.3 CGD-ASYINT00301-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate V<sub>DD</sub> AIB side castellation as shown below.

#### CGD-ASYINT00301-01: GS6530-2L DFN 8x8 .. To .. CGD65A130S2 DFN8x8

| Packaging                   | CGD65A130S2         | GS6530-2L                                | Notes                       |

|-----------------------------|---------------------|------------------------------------------|-----------------------------|

| DFN8x8 mm                   | 1                   | 5,6,7,8                                  |                             |

|                             | 2                   | 5,6,7,8                                  |                             |

| 1-8 Drain                   | 3                   | 5,6,7,8                                  |                             |

| 9-12 Source<br>13 Kelvin    | 4                   | 5,6,7,8                                  |                             |

| 14 Gate<br>15 Current Sense | 5                   | 5,6,7,8                                  |                             |

| 16 V <sub>dd</sub>          | 6                   | 5,6,7,8                                  |                             |

|                             | 7                   | 5,6,7,8                                  |                             |

|                             | 8                   | 5,6,7,8                                  |                             |

|                             | 9                   | 1,2,9                                    |                             |

|                             | 10                  | 1,2,9                                    |                             |

| 3.                          | 11                  | 1,2,9                                    |                             |

|                             | 12                  | 1,2,9                                    |                             |

|                             | 13                  | 3                                        | C1 Pin2, Side Castellation  |

| 1                           | 14                  | 4                                        |                             |

| 3                           | 15                  | NC                                       | Side Castellation           |

| 16 15 14 13                 | 16                  | NC                                       | C1 Pin 1, Side Castellation |

|                             | Notes: NC -<br>C1 - | Not connected<br>0.1uF 50V X7R 0603 MLCC |                             |

Figure 9 - CGD-ASYINT00301-01 AIB Pin-Definition

#### 4.4 CGD-ASYINT00401-01 AIB

#### This AIB requires a separate $V_{DD}$ connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure  $V_{DD}$  connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate  $V_{\text{DD}}$  AIB side castellation as shown below.

#### Packaging DFN8x8 mm CGD65A130S2 IPP60R099P7 2, Tab 2 2, Tab 2, Tab 4 2, Tab 2, Tab 6 2, Tab 2, Tab 8 2, Tab C1 Pin1 10 3 11 12 3 13 NC PTH 14 1 15 PTH C1 Pin2 & PTH 16 NC 4.7uF 50V X7R 0603 MLCC Plated Through Hole Not connected

CGD-ASYINT00401-01: IPP60R099P7 TO220 .. To .. CGD65A130S2 DFN8x8

Figure 10 - CGD-ASYINT00401-01 AIB Pin-Definition

#### 4.5 CGD-ASYINT00501-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate V<sub>DD</sub> AIB side castellation as shown below.

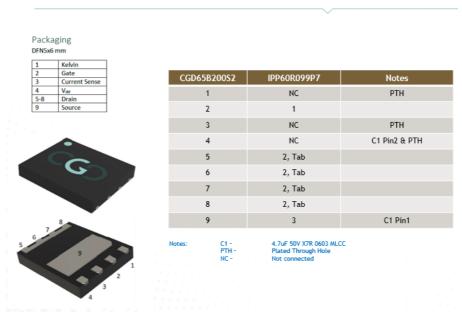

**CGD-ASYINT00501-01:** IPP60R099P7 TO220 .. To .. CGD65A200S2 DFN5x6

Figure 11 - CGD-ASYINT00501-01 AIB Pin-Definition

#### 4.6 CGD-ASYINT00601-01 AIB

This AIB does NOT require a separate  $V_{\text{DD}}$  connection from the customer/recipient PCB. The AIB/CGD device takes its  $V_{\text{DD}}$  signal directly from the recipient PCB footprint.

#### CGD-ASYINT00601-01: NV6115 QFN5x6 .. To .. CGD65B200S2 DFN5x6

| 1 Kelvin<br>2 Gate                   | CGD65B200S2                     | NV6115                                                      | Notes    |

|--------------------------------------|---------------------------------|-------------------------------------------------------------|----------|

| 3 Current Sense<br>4 V <sub>66</sub> | 1                               | NC                                                          | C1 Pin 1 |

| 5-8 Drain                            |                                 |                                                             | CIPILI   |

| 9 Source                             | 2                               | 2                                                           |          |

|                                      | 3                               | NC                                                          |          |

|                                      | 4                               | 1                                                           | C1 Pin 2 |

|                                      | 5                               | 5,6,7,8                                                     |          |

| 6                                    | 6                               | 5,6,7,8                                                     |          |

|                                      | 7                               | 5,6,7,8                                                     |          |

|                                      | 8                               | 5,6,7,8                                                     |          |

| 8                                    | 9                               | S                                                           |          |

| 7 8 9 9                              | Notes: NC -<br>NV6115 -<br>C1 - | Not connected<br>Pins 3,4 are NC<br>0.1uF 50V X7R 0603 MLCC |          |

Figure 12 - CGD-ASYINT00601-01 AIB Pin-Definition

#### 4.7 CGD-ASYINT00701-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate V<sub>DD</sub> AIB side castellation as shown below.

#### CGD65A130S2 IPL60R065P7 Packaging DFN8x8 mm 2 5 5 8 Side Castellation 3,4 10 11 13 2 C1 Pin 1 14 15 Side Castellation NC C1 Pin 2, Side Castellation 16 NC -C1 -Not connected 0.1uF 50V X7R 0603 MLCC

CGD-ASYINT00701-01: IPL60R065P7 ThinkPAK8x8 .. To .. CGD65A130S2 DFN8x8

Figure 13 - CGD-ASYINT00701-01 AIB Pin-Definition

#### 4.8 CGD-ASYINT00801-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate V<sub>DD</sub> AIB side castellation as shown below.

Figure 14 - CGD-ASYINT00801-01 AIB Pin-Definition

#### 4.9 CGD-ASYINT00901-01 AIB

This AIB does NOT require a separate  $V_{\text{DD}}$  connection from the customer/recipient PCB. The AIB/CGD device takes its  $V_{\text{DD}}$  signal directly from the recipient PCB footprint.

#### CGD-ASYINT00901-01: NV6125 QFN 6x8 .. To .. CGD65A130S2 DFN8x8

| Pac      | kaging                                       | CCD4E 1420C2 | NB/C43E                                 | Maria                       |

|----------|----------------------------------------------|--------------|-----------------------------------------|-----------------------------|

|          | x8 mm                                        | CGD65A130S2  | NV6125                                  | Notes                       |

|          |                                              | 1            | 15-23                                   |                             |

| 1-8      | Drain                                        | 2            | 15-23                                   |                             |

| 9-12     | Source<br>Kelvin                             | 3            | 15-23                                   |                             |

| 14       | Gate                                         | 4            | 15-23                                   |                             |

| 15<br>16 | Current Sense                                | 5            | 15-23                                   |                             |

|          |                                              | 6            | 15-23                                   |                             |

|          |                                              | 7            | 15-23                                   |                             |

|          |                                              | 8            | 15-23                                   |                             |

|          |                                              | 9            | 2,3,4,5,6, CP                           |                             |

|          |                                              | 10           | 2,3,4,5,6, CP                           |                             |

|          | 8                                            | 11           | 2,3,4,5,6, CP                           |                             |

|          |                                              | 12           | 2,3,4,5,6, CP                           |                             |

|          |                                              | 13           | 2,3,4,5,6, CP                           | C1 Pin 1                    |

|          | S                                            | 14           | 27                                      |                             |

|          | 14 13                                        | 9 15         | NC                                      | Side Castellation           |

|          | 16 <sup>15</sup> <sup>14</sup> <sup>13</sup> | 16           | 28                                      | C1 Pin 2, Side Castellation |

|          | 16 15                                        | Notes: NC -  | Not connected<br>0.1uF 50V X7R 0603 MLC |                             |

Figure 15 - CGD-ASYINT00901-01 AIB Pin-Definition

#### CGD-ASYINT01001-01 AIB

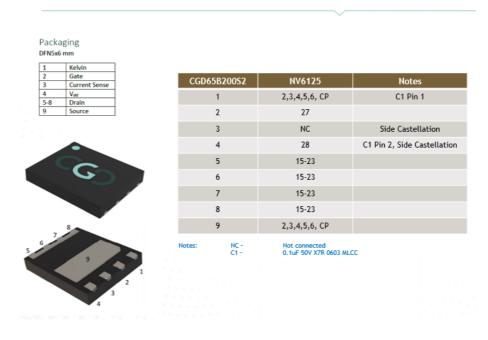

This AIB does NOT require a separate V<sub>DD</sub> connection from the customer/recipient PCB. The AIB/CGD device takes its V<sub>DD</sub> signal directly from the recipient PCB footprint.

#### CGD-ASYINT01001-01: NV6125 QFN 6x8 .. To .. CGD65A200S2 DFN5x6

Figure 16 - CGD-ASYINT01001-01 AIB Pin-Definition

#### 4.11 CGD-ASYINT01101-01 AIB

#### This AIB requires a separate V<sub>DD</sub> connection from the customer/recipient PCB to power the CGD device.

Please ensure to connect a safe & secure V<sub>DD</sub> connection between an appropriate voltage reference node on the customer/recipient PCB design to the appropriate V<sub>DD</sub> AIB side castellation as shown below.

CGD-ASYINT01101-01: GS-065-011-1-L DFN 5x6 .. To .. CGD65A200S2 DFN5x6

### Packaging GS-065-011-1-L Current Se C1 Pin 1 2 NC Side Castellation NC C1 Pin 2, Side Castellation 4 6 Not connected 0.1uF 50V X7R 0603 MLCC

Figure 17 - CGD-ASYINT01101-01 AIB Pin-Definition

#### 4.12 CGD-ASYINT01201-01 AIB

This AIB does NOT require a separate  $V_{\text{DD}}$  connection from the customer/recipient PCB. The AIB/CGD device takes its  $V_{\text{DD}}$  signal directly from the recipient PCB footprint.

#### CGD-ASYINT01201-01: NV6128 QFN 6x8 .. To .. CGD65A130S2 DFN8x8

| Packaging<br>DFN8x8 mm      | CGD65A130S2         | NV6128                                   | Notes                       |

|-----------------------------|---------------------|------------------------------------------|-----------------------------|

| DFN8X8 mm                   | 1                   | 15-23                                    |                             |

| 1-8 Drain                   | 2                   | 15-23                                    |                             |

| 9-12 Source<br>13 Kelvin    | 3                   | 15-23                                    |                             |

| 14 Gate<br>15 Current Sense | 4                   | 15-23                                    |                             |

| 16 V <sub>66</sub>          | 5                   | 15-23                                    |                             |

|                             | 6                   | 15-23                                    |                             |

|                             | 7                   | 15-23                                    |                             |

|                             | 8                   | 15-23                                    |                             |

|                             | 9                   | 2,3,4,5,6, CP                            |                             |

| 111111                      | 10                  | 2,3,4,5,6, CP                            |                             |

| 8                           | 11                  | 2,3,4,5,6, CP                            |                             |

|                             | 12                  | 2,3,4,5,6, CP                            |                             |

|                             | 13                  | 9,29                                     | C1 Pin 1                    |

| 5                           | 14                  | 27                                       |                             |

|                             | 9 15                | NC                                       | Side Castellation           |

| 16 15 14 13                 | 16                  | 28                                       | C1 Pin 2, Side Castellation |

| 16 15                       | Notes: NC -<br>C1 - | Not connected<br>0.1uF 50V X7R 0603 MLCC |                             |

Figure 18 - CGD-ASYINT01201-01 AIB Pin-Definition

# Figure List

| Figure 1 – Bare AIB on PCB Panel                    | 5  |

|-----------------------------------------------------|----|

| Figure 2 - AIB Mounted to a Recipient PCB Assembly  | 6  |

| Figure 3 - CGD DFN 5x6 Package                      | 7  |

| Figure 4 - CGD DFN 8x8 Package                      | 7  |

| Figure 5 - AIB Construction Showing Internal Layers | 7  |

| Figure 6 - Typical AIB Electrical Schematic         |    |

| Figure 7 - CGD-ASYINT00101-01 AIB Pin-Definition    |    |

| Figure 8 - CGD-ASYINT00201-01 AIB Pin-Definition    | 12 |

| Figure 9 - CGD-ASYINT00301-01 AIB Pin-Definition    | 13 |

| Figure 10 - CGD-ASYINT00401-01 AIB Pin-Definition   | 14 |

| Figure 11 - CGD-ASYINT00501-01 AIB Pin-Definition   | 15 |

| Figure 12 - CGD-ASYINT00601-01 AIB Pin-Definition   | 16 |

| Figure 13 - CGD-ASYINT00701-01 AIB Pin-Definition   |    |

| Figure 14 - CGD-ASYINT00801-01 AIB Pin-Definition   |    |

| Figure 15 - CGD-ASYINT00901-01 AIB Pin-Definition   | 19 |

| Figure 16 - CGD-ASYINT01001-01 AIB Pin-Definition   | 20 |

| Figure 17 - CGD-ASYINT01101-01 AIB Pin-Definition   | 21 |

| Figure 18 - CGD-ASYINT01201-01 AIB Pin-Definition   | 22 |

## **Appendices**

#### **AIB Variants**

Table shown correct at document release date although further variants will be added as required. Please contact CGD for full details.

| Recipient Interface |             | CGD Interface     | CGD Ordering Part Number |                    |

|---------------------|-------------|-------------------|--------------------------|--------------------|

| GaN Systems         | GS66508B    | GaN <sub>PX</sub> | DFN 8x8                  | CGD-ASYINT00101-01 |

| GaN Systems         | GS065011-1L | PDFN 8x8          | DFN 5x6                  | CGD-ASYINT01101-01 |

| GaN Systems         | GS6530-2L   | PDFN 8x8          | DFN 8x8                  | CGD-ASYINT00301-01 |

| Infineon            | IPP60R099P7 | T0-220            | DFN 8x8                  | CGD-ASYINT00401-01 |

| Infineon            | IPP60R099P7 | T0-220            | DFN 5x6                  | CGD-ASYINT00501-01 |

| Infineon            | IPL60R065P7 | ThinPAK 8x8       | DFN 8x8                  | CGD-ASYINT00701-01 |

| Innoscience         | INN650D02   | PDFN 8x8          | DFN 5x6                  | CGD-ASYINT00801-01 |

| Navitas             | NV6115      | QFN 5x6           | DFN 5x6                  | CGD-ASYINT00601-01 |

| Navitas             | NV6115      | QFN 5x6           | DFN 8x8                  | CGD-ASYINT00201-01 |

| Navitas             | NV6125      | QFN 6x8           | DFN 8x8                  | CGD-ASYINT00901-01 |

| Navitas             | NV6125      | QFN 6x8           | DFN 5x6                  | CGD-ASYINT01001-01 |

| Navitas             | NV6128      | QFN 6x8           | DFN 8x8                  | CGD-ASYINT01201-01 |

Table 2 - All Available Variants of AIB

### Dare to innovate differently

#### **Cambridge GaN Devices Limited**

Deanland House 160 Cowley Road Cambridge CB4 0DL

#### Disclaimer

Information presented here by Cambridge GaN Devices Limited is believed to be correct and accurate. Cambridge GaN Devices Limited shall not be liable to any recipient or third part for any damages, including (but not limited to) personal injury, property damage, loss of profits, loss of business opportunity, loss of use, interruption of business, or indirect, special, incidental or consequential damages of any kind in connection with, or arising from, the use or performance of the data herein.

No obligation or liability to the recipient or third part shall arise from Cambridge GaN Devices Limited providing technical or other services.